## Parallel matrix computations

(Gentle intro into a part of HPC)

#### Miroslav Tůma

Faculty of Mathematics and Physics

Charles University

mirektuma@karlin.mff.cuni.cz

Praha, April 23, 2025

#### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- 4 Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

- Sparse data decomposition: graph partitioning

- 9 Factorizations

- Parallel and parallelized algebraic preconditioning

## Introductory notes

- Created as a material supporting online lectures of NMNV532.

- Assuming basic knowledge of principles of numerical mathematics:

- matrix-matrix and matrix-vector multiplication, factorizations,

- algebraic iterative (Krylov space) and

- direct (dense) solvers (elimination/factorization/solve)

#### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- 4 Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

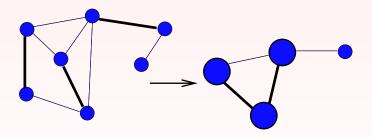

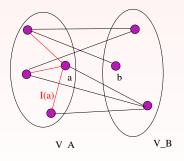

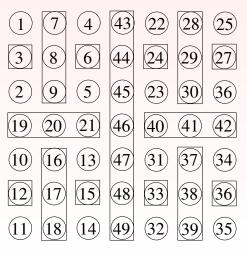

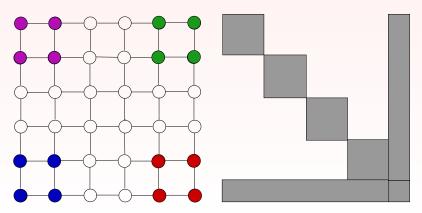

- 8 Sparse data decomposition: graph partitioning

- 9 Factorizations

- Parallel and parallelized algebraic preconditioning

## Basic terminology related to this text

#### Tools used to compute (process data, perform computations)

- Computer: device able to perform (process) automatically sequences of arithmetic or logical instructions.

- Computation (data processing). Controlled by program or code.

- Modern computers consist of one or more of data/program/code processing units called also processors.

- If only one processor: CPU (central processing unit).

## Basic terminology related to this text

#### Tools used to compute (process data, perform computations)

- Chip: physical unit on which one or more processors reside.

- Processors typically structured: contain one, but rather more units called cores.

- Computer architecture: more detailed specification of the considered computer system.

## Basic terminology related to this text II

#### Tools used to compute (process data, perform computations) II

- Clock (clock generator, timer): signal used to coordinate actions of processors and digital circuits.

- Clock rate / frequency: frequency on which the computer clock is running. Another way to describe processor/processors speed: cycle time.

- Data and programs are stored in memory.

- Memory is typically structured and hierarchically organized

## Basic terminology related to this text III

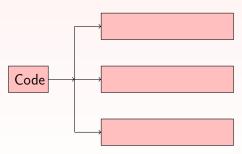

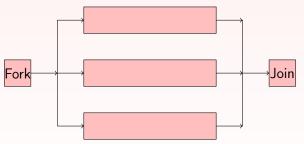

#### Splitting computation into smaller pieces

- Computation typically decomposed into smaller items tasks, subtasks, instructions, stages.

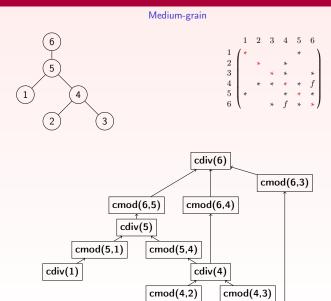

- Approximate size of tasks: granularity. We distinguish large grain, medium grain or small grain size of tasks.

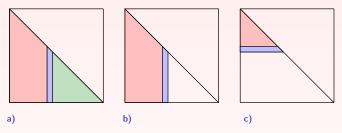

- Examples of large and medium grain:

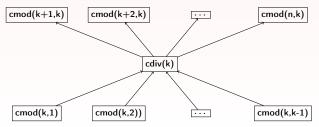

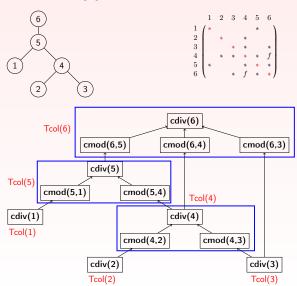

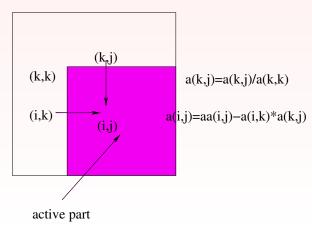

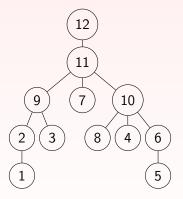

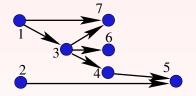

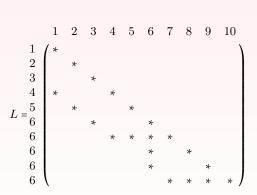

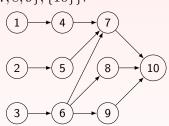

#### Numerical Cholesky factorization: from operations to tasks

- $\bullet$  cdiv(k): scaling column k by the square root of the diagonal entry

- $\bullet$  cmod(j,k): column j modified by a multiple of column k

#### Algorithm

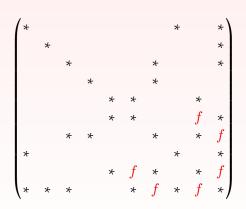

# Algorithm Sparse column (left-looking) Cholesky 1: for j = 1:n do 2: for $k \in Struct(L_{j*})$ do 3: cmod(j,k)4: end for 5: cdiv(j)6: end for

#### Numerical Cholesky factorization: from operations to tasks

- $\bullet$  cdiv(k): scaling column k by the square root of the diagonal entry

- $\bullet$  cmod(j,k): column j modified by a multiple of column k

#### Algorithm

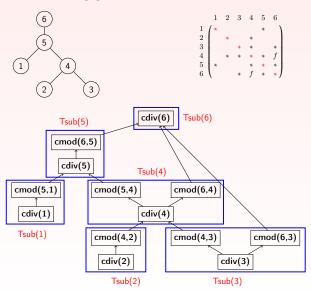

#### Sparse submatrix (right-looking) Cholesky

```

Sparse submatrix (right-rooking)

1: for k = 1 : n \ do

2: cdiv(k)

3: for j \in Struct(L_{*k}) \ do

4: cmod(j,k)

5: end \ for

6: end \ for

```

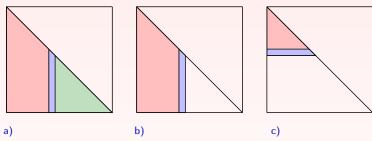

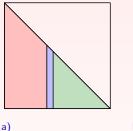

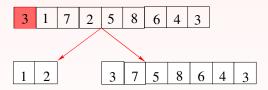

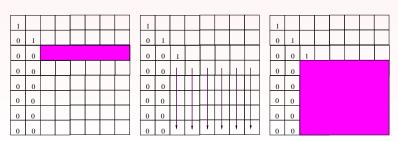

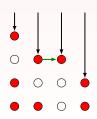

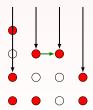

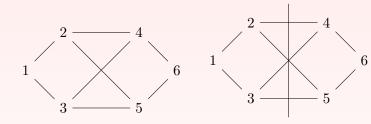

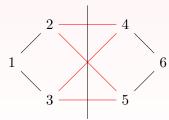

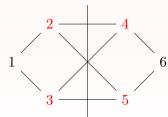

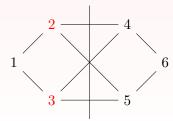

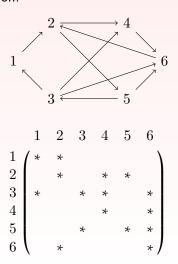

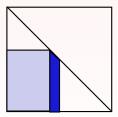

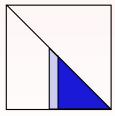

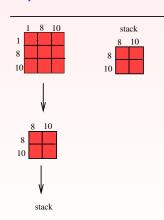

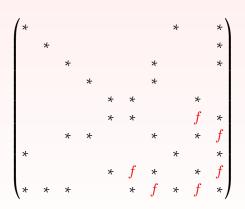

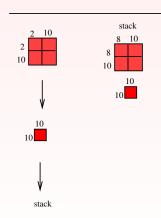

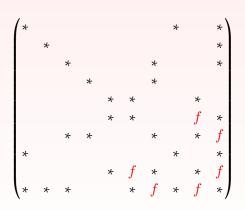

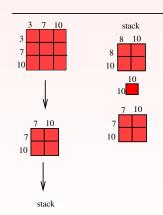

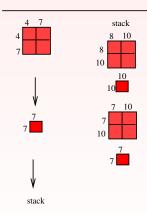

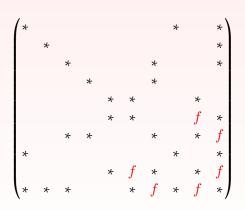

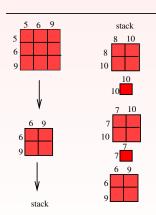

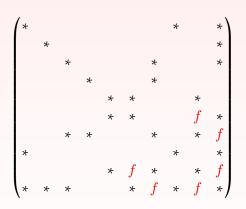

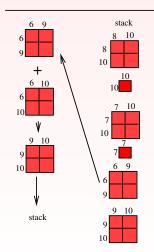

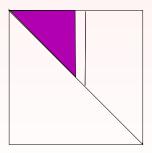

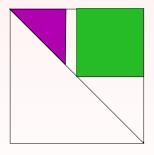

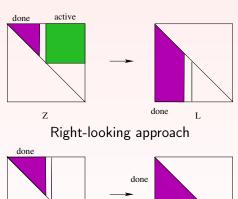

Splitting Cholesky factorization into tasks

- ullet cdiv(k): scaling column k by the square root of the diagonal entry

- ullet cmod(j,k): column j modified by a multiple of column k

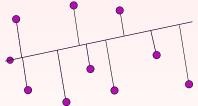

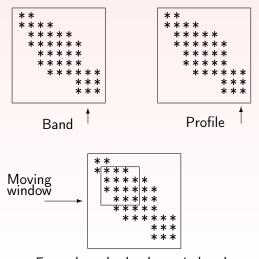

Large-grain column communication model

Large-grain submatrix communication model

cdiv(2)

cdiv(3)

## Basic terminology related to this text III

#### Splitting computation into smaller pieces

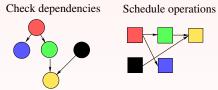

- The tasks assigned to computational units: processes or threads.

- Threads: programmed instructions bundled with data, to be managed by a scheduler.

- Mapping between the processes/threads and the computational environment is called scheduling.

- In order to achieve a correct data flow: processes need to be synchronized:

- by computer

- by ourselves

## Basic terminology related to this text IV

#### Communication

Any computation process needs to communicate. At least internally.

- Communication: internal (as communication with memory) or external (as I/O (input/output).

- Communication based on an embedded communication network (links) (hardware) and programs (software).

- Communication characteristics:

- ► Bandwidth: rate at which a link (links) can transmit data.

- Latency describes a delay (amount of time) from input to the desired outcome/output. There are more different types of latencies: (processor-memory, network, internet, router, storage etc.) and we will mention some of them separately.

The most important characteristics of communication (from our point of view): latency and bandwidth.

# Basic terminology related to this text V

#### Measuring computational performance

- flop (number of floating-point operations),

- flops (number of floating point operations per second; also plural of flop)

- communication latencies (memory-processors, processor-processor, and so on)

- Everything together: performance

- All important parameters should be involved in timing models

- The timing models described here are extremely simplified.

#### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- 4 Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

- 8 Sparse data decomposition: graph partitioning

- 9 Factorizations

- Parallel and parallelized algebraic preconditioning

#### What is parallel computing and parallel computer

- Parallel computer: a set of processing, cooperating and communicating elements

- Potential parallelism: property of an application and of an algorithm to solve the computational problems.

- Parallel computing: ability of concurrent (simultaneous) computation/ data processing on more computational units. These units can be represented by more CPUs. Also other centralized or detached computational resources can perform the computational tasks simultaneously.

#### What is parallel computing and parallel computer

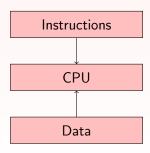

- Traditional serial or sequential computation is based on data processing on a single machine (computer/chip etc.) using either a single Central Processing Unit (CPU) or a single computational element. Now extinct. Still called here uniprocessor.

- Ways to increase the power:

- more complex logic of the processor/chip: like more transistors on chip

- faster clock

- In any case, sequential computation and cannot go too far even with such enhancements: single processors are not enough

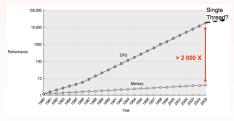

#### Why parallel processing is of of interest: three questions?

- Q 1: Why single processors are not enough?

- Consider the computational power measured by the number of transistors on a chip (this was often used approximate method to measure the computational power).

- 1971: chip 4004 : 2.3k transistors

- 1978: chip 8086 : 31k transistors (2 micron technology)

- 1982: chip 80286: 110k transistors (HMOS technology)

- 1985: chip 80386: 280k transistors (0.8 micron CMOS)

- 1989: chip 80486: 1.2M transistors

- 1993: Pentium: 3.1M transistors (0.8 micron biCMOS)

- 1995: Pentium Pro: 5.5M (0.6 micron)

- 1997: Pentium II: 7.5M transistors

- 1999: Pentium III: 24M transistors

- 2000: Pentium 4: 42M transistors

- 2002: Itanium: 220M transistors

- 2003: Itanium 2: 410M transistors

#### Why parallel processing is of of interest: three questions?

- Earlier chips: performance improvement strongly correlated to the number of transistors and to the clock frequency.

- Performance improvement of single processors since 2002 only 20% per year,

- It has been approximately 50% per year between 1986 and 2002.

- Since 2003: difficulties to increase transistor density on a single computational unit on a chip. The clock frequency increase has started to stagnate.

#### Why parallel processing is of of interest: three questions?

- Since around 2003 (as AMD 64 Athlon X2, Intel Core Duo): more "independent" computational units (cores)

- Explanations are technologically oriented.

- This trend goes on.

- 2023: Apple A17: 19G transistors (3nm technology)

- 2023: Apple M2 Ultra: 134G transistors (5nm technology)

- 2023: AMD Instinct: 146G transistors (5nm technology)

$\ensuremath{\mathsf{Q}1}$  - answer: sequential processing has inherent physical limitations. What are these physical limitations?

#### 1. Finite signal speed

Consider the cycle time (time per computer clock tick) and the clock rate (frequency of clock ticks). Then, e.g., the frequency

$100 \ MHz$  corresponds to  $10 \ ns$

- The frequency of 2~GHz then correspond to  $0.5~\rm ns.$  The finite signal speed (speed of light of  $3.10^8~ms^{-1}$ ), implies:

- With the cycle time 1 ns (frequency  $1\ GHz$ ) signal can pass at most cca  $30\ cm$  per the cycle time.

- With the cycle time 1 ps (frequency 1 Tflops) signal can reach at most the radius < c/rate  $\approx 0.3$  mm

#### 1. Finite signal speed

- An example of wiring in computers shows that the speed can be critical:

- Early and very mildly parallel computer Cray 2 (1981) had about 10 km of interconnecting wires.

- "Small" physical size of processors does not decrease the role of insufficient signal speed in practice at high frequencies:

#### 1. Finite signal speed

- Historical demonstration of increased clock rates:

- ▶ 1941: Z3 (Konrad Zuse) 5 10 Hz

- 1958: First integrated circuit: flip-flow with two transistors (built by Jack Kilby, Texas Instruments)

- ▶ 1969: CDC 7600: 36.4 MHz (27.5 ns cycle time) (considered as the fastest computer until 1975)

- ▶ 1976: Cray-1: 80 MHz (12.5 ns cycle time) (but throughput faster more than 4 times than for CDC 7600)

- ▶ 1981: IBM PC: 4.77 MHz

- ▶ 2011: AMD FX-8150 (Bulldozer) chips: cca 8.81 GHz (cca 0.12 ns)

- 2022: Intel Core i9-13900K (3 GHz, up to 5.80 GHz in turbo mode ☺)

#### 2. Limits in memory density

- Consider  $1\ TB$  of memory. On a chip of circular shape and area of  $\pi r^2$ , where r =  $0.3\ mm$  (from above, for 1 ps clock rate).

- This circular area implies: an approximate size 3.5 Ångström $^2$  =  $3.5 \times 0.01$   $nm^2$  for one bit of information. And remind that

- A typical protein is about 5 nm in diameter,

- ▶ a molecule of glucose is just about 0.1 nm in diameter.

- Hence: we are close to absolute limits of affordable density to store information.

#### 3. Technology and lithography limits

- Production limits from possibilities of the electron-beam lithography.

- ullet Early lithography resolution has been for Intel 4004 chips  $10~\mu m$ .

- Later Intel processors as: Xeon Phi (22nm | lithography resolution), SPARC M7 (20 nm), contemporary GPUs (28nm), More new chips around 2020: 5nm lithography (Apple A14 Bionic, Apple M1, etc.), getting even more below (see above)

- Changing technology: SSI (1964), MSI (1968), LSI (1971), VLSI (1980), ULSI, WSI, SoC, 3D-IC etc. But the pace of advancements slows down.

- Size of atoms and quantum effects as quantum tunelling seem to ultimately limit this progress.

#### 4. Power and heat dissipation

- Transistor speed increases: new features need more transistors

- The corresponding power increases.

$$P_{CPU} = P_{dyn(switching)} + P_{short\ circuits} + P_{static(leakage)}$$

logic gates, toggle gate current, leak - among differently doped parts

- Global overall guess

- $P_{CPU}$ : switching-const × area-const × frequency ×  $voltage^2$

- Power (heat dissipation) density has been growing exponentially because of increasing clock frequency and doubling of transistor count.

- Consequently, processors with a clock rate  $\gg 3.3 GHz$  are difficult and costly to be cooled using contemporary cooling techniques.

#### 5. Some related early predictions

- R. Dennard, 1974: scaling law roughly stating that chip power requirements are proportional to area of the chip (Dennard (MOSFET) scaling)

- Since cca 2005 this rule seems to be not valid anymore. Strong motivation to develop multicore processors.

#### 5. Some related early predictions

- Patrick Gelsinger, 2001: if scaling continues at present pace, by 2005, high speed processors would have power density of nuclear reactor, by 2010, a rocket nozzle, and by 2015, surface of sun.

- Cooling is needed.

- Hot integrated circuits become unreliable.

- We start to get dark silicon part of circuitry of an integrated circuit

that cannot be powered at the nominal operating voltage given a

thermal dissipation constraint.

- But, nowadays, instead of wasting the dark silicon, the energy can be used to run specialized cores: cores able to perform a small set of tasks at significantly lower energy

Q2: is it technologically possible to build the new and still more powerful parallel computational systems?

- It might seem that processor technologies are getting better steadily and very fast,

- It might seem that computers based on these technologies are getting much faster.

- Consider the power of processors expressed via number of transistors on (chips / microprocessors / integrated circuits) expressed via an empirical observation and prediction called Moore's law:

Q2: is it technologically possible to build the new and still more powerful parallel computational systems?

#### Observation

Moore's law: The number of transistors per square inch on integrated circuits doubles approximately from one to two years since the integrated circuit was invented (1965, Gordon E. Moore, co-founder of Intel recalibrated to two years in 1975)

- The law is sometimes restated that chip performance doubles every 18 months (David House, Intel executive, 1975) which combines the effect of more transistors on chip and having the transistors faster

- Dennard's scaling --> power per Joule increases in this way; many more "laws".

#### Corollary

Number of cores will double every 18 months (A. Agrawal, MIT, 2009)

#### Q2: Sketch of subsequent development

- 2005: Pentium D:230M+ transistors

- 2007: AMD K2 quad core 2M L3: 463M transistors

- 2007: IBM POWER6: 789M transistors

- 2008: Intel Core i7 quad: 731M transistors

- 2008: AMD K10 quad core 6M L3: 758M transistors

- 2009: AMD Six core Opteron 2400: 904M transistors

- 2010: Intel Six-Core Core i7 (Gulftown): 1170M transistors

- 2011: Six-Core Core i7/8-Core Xeon E5 (Sandy Bridge-E/EP): 2270M transistors

- 2012: Intel 8-Core Itanium Poulson: 3100M transistors

- 2013: Microsoft/AMD Xbox One Main SoC: 5000M transistors

- 2015: Sparc M7 (64-bit, SIMD, caches), Oracle, 10G transistors

- 2019: AWS Graviton2 (64-bit, 64-cores, SIMD, caches), Amazon, 30G transistors

- 2023: Apple A17: 19G transistors (3nm technology)

- 2023: Apple M2 Ultra: 134G transistors (5nm technology)

- 2023: AMD Instinct: 146G transistors (5nm technology)

The Moore's law even after 2003. But Far beyond uniprocessor status.

#### Q2: Graphic processing units

- 1997: Nvidia NV3: 3.5M transistors

- 1999: AMD Rage 128: 8M transistors

- 2000: Nvidia NV11: 20M transistors

- 2000: Nvidia NV20: 57M transistors

- 2001: AMD R200: 60M transistors

- 2002: AMD R300: 107M transistors

- 2004: Nvidia NV40: 222M transistors

- etc.

- 2012: Nvidia GK110 Kepler: 7080M transistors

- 2013: AMD RV1090 or RV1170 Hawai: 6300M transistors

- 2015: Nvidia GM200 Maxwell: 8100M transistors

- 2018: TU106 Turing, Nvidia, 10.8G transistors

- 2019: Navi10, AMD, 10.3G transistors

- FPGA (field-programmable gate array) up to 20G transistors in 2014

# Q2: is it technologically possible to build the new and still more powerful parallel computational systems?

- Despite enormous technological progress there are more predictions that the Moore's law will cease to be valid around 2025. Slowing down? Doubling the number of transistirs each three years? (Pat Gelsinger, 2023)?

- Technological point of view is more positive: Using more processing units can actually result in high gains. It comes with some economy of scaling. Using more processing units (processors, cores) can overcome the problems summarized above, can be efficient for problem solving and can be rather cost efficient.

Q2: partial answers

#### Observation

Grosch's law: To do a calculation 10 times as cheaply you must do it 100 times as fast (H. Grosch, 1965; H.A. Grosch. High speed arithmetic: The digital computer as a research tool. (1953); H.A. Grosch. Grosch's law revisited. (1975)). Another formulation: The power of computer systems increases as the square of their cost.

Consequently, computers should obey the square law:

#### Observation

When the price doubles, you should get at least four times as much speed (similar observation by Seymour Cray, 1963).

### Why parallel processing is of of interest: three questions?

Q3: Are the parallel systems really needed?

- Computation of climate models (systems of differential equations simulating interactions of atmosphere, oceans, ice, land surface: far more accurate models needed; global 3D models needed

- Computation of re-entry corridor to get back to the terrestrial atmosphere: supersonic flow, Boltzmann equations

- Protein folding: misfolded proteins: Parkinson and Alzheimer

- Energy research: combustion, solar cells, batteries, wind turbines ⇒ large ODE systems

- Crash-tests: the need to solve large systems of nonlinear equations

- Computation of turbulent flows: large systems of PDEs in 3D.

- Big data analysis: LHC, medical imaging etc.

- Summarizing: 3D space/ time eats up the increase in power of today's computers

### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

- Sparse data decomposition: graph partitioning

- 9 Factorizations

- Parallel and parallelized algebraic preconditioning

- Why we cannot write codes that automatically parallelize? Could we rely on high-quality software technologies to convert the programs for parallel computations?

- Why this is of interest for mathematicians?

An answer to such questions: parallel programming (coding).

- There is a very limited success in converting programs in serial languages like C and C++ into parallel programs

- For example, multiplication of two square matrices can be viewed as a sequence of linear combinations or a sequence of dot products.

Sometimes is better the first, sometimes the second.

- Dot products may be very time consuming on some particular parallel computer architectures

- In processing sparse data structures efficiently automatic techniques cannot be often used at all

- Codes have to be often tightly coupled with particular applications in mind

- Parallelization may not be obtained by parallelizing individual steps.

Instead, new algorithms should be devised.

- This is a strictly mathematical step and it is very difficult to automatize.

- Often very different techniques needed for moderate number of cores on one side and large number of cores on the other side.

- Parallelism can be very different, as task-driven or even data-driven as we will see later.

- Automatizing processes may help, but often not sufficiently enough.

Still new hardware/software concepts being developed.

- Lower precision plus parallelism?

- Computations and AI?

### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- 4 Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

- 8 Sparse data decomposition: graph partitioning

- 9 Factorizations

- 10 Parallel and parallelized algebraic preconditioning

- 1. Levels of parallelism historical examples a very brief sketch

- Long time ago recognized that:

- Parallelism saves power (electricity+power+cooling → less than 50 percent of operating costs (apc.com, 2003)),

- improves chip yield,

- and simplifies verification.

- Nowadays: more motivations

- Let us mention some historical milestones

- 1. Levels of parallelism historical examples a very brief sketch

- running jobs in parallel for reliability IBM AN/FSQ-31 (1958) some of them were purely duplex machine (time for operations  $2.5\mu$  s 63.5  $\mu$  s; history of the word byte)

- running parts of jobs on independent specialized units UNIVAC LARC (1960) – first I/O processor, world most powerful computer 1960-1961; interleaved access to memory banks

- running different jobs in parallel for speed

Burroughs D-825 (1962) more modules, job scheduler; multiple computer systems

- running parts of programs in parallel Bendix G-21 (1963), CDC 6600 (1964) – nonsymmetric multiprocessor; silicon-based transistors; first RISC; predecessor of I/O multithreading, 10 parallel functional units

- 1. Levels of parallelism historical examples a very brief sketch

- development of multitasking with fast switching: threads: 'light-weight' tasks sharing most of resources, typically inside a process, managed by the operating system scheduler.

- running matrix-intensive stuff separately development of complex IBM 704x/709x (1963); facilities STAR 100, ASC TI (1965); 20MFLOPs ALU

- matrix processors

- co-processors

- use of various recursive schemes for arithmetic operations performed separately

- 1. Levels of parallelism historical examples a very brief sketch

- parallelizing instructions

IBM 709 (1957), IBM 7094 (1963)

- data synchronizer units DSU → channels enable simultaneously read/write/compute

- overlap computational instructions / loads and stores

- IBR (instruction backup registers)

- instruction pipeline by splitting instructions in segments

- so we have finally two basic ways for splitting to segments: data pipeline and instruction pipeline

- 1. Levels of parallelism historical examples a very brief sketch

- parallelizing arithmetics: less and less clocks per instruction

- Bundling instructions and data: prescheduling as VLIW (very long instruction word) Can describe a rather complex static operations.

- Nowadays: concept of threads

- ★ Multiflow Trace (1984), then in IA64 architecture (Intel)

- ★ sophisticated software optimization, simpler decode and schedule ©

- ★ difficult to predict dynamic events like missing data in local memories ②

- ► Superscalar in RISC (CDC6000): operations scheduled at run-time

- ø bit-level parallelism

What we can expect as HW features nowadays

- 2. Processing features in contemporary parallel computations

- FPU and ALU work in parallel

- One of the first type of parallelism: ALU (arithmetic-logical unit) separated from FPU (floating-point unit)

- Cray-1 (1976) and its predecessors: ALU (arithmetic-logical unit)

rather weak

- Strengthening ALU and simplifying processors pushed in 1980's development of successful workstations.

#### 2. Processing features in contemporary parallel computations

- CISC and RISC

- move from CISC (complex instruction set) to RISC (reduced instruction set) performed in 1980's. One of the reasons: sophisticated hardware for instruction decoding.

- The idea behind RISC: it is better to have less and much more optimized instructions.

- Also, this enabled to increase the clock rates

- ► Technological progress has brought efficient CISCs back ©

- But still, nowadays, a lot of processors perform internally a transformation of CICS into RISC instructions.

### 2. Processing features in contemporary parallel computations

- Pipeline for instructions

- ▶ Partition an instruction into several segments called a pipeline

- pipelining instructions: an efficient form of parallelism within a single processor

- Consequently, more instructions can be processed concurrently processing different segments of different instructions in parallel.

#### An example: of standardized RISC instruction pipeline:

- Instruction fetch (fetches the instruction from memory)

- Instruction decode and register fetch (decode the fetched instruction)

- Fetch operands

- Execute operations

- Register write back.

#### This implies a possible overlap

### 2. Processing features in contemporary parallel computations

### 3 Pipeline for instructions - continued

- First use of pipelining: ILLIAC II (1962) project, IBM Stretch project, IBM 7094 (1969). Conceived even earlier: in the Z1 (1938) and the Z3 (1941) computers by Konrad Zuse.

- Contemporary processors can have from a few up to small tens of stages (superpipelined processors).

- Compiler task is to prepare instructions such that they can be efficiently pipelined. Pipeline delay due to waiting for data is called that the pipeline stalls. This is what must be avoided.

- Nowadays: instruction pipelines everywhere.

- 2. Processing features in contemporary parallel computations

- Pipeline for data

- Pipelining data:

- Instead of segmenting instructions we can partition operations

An example: adding two floating-point numbers.

- check exponents

- possibly swap operands

- possibly shift one of mantissas by the number of bits determined by differences in exponents

- compute the new mantissa

- normalize the result

Pipelining operations we get to the concept of program vectorization

- 2. Processing features in contemporary parallel computations

- Overlapping operations

- Generalization of instruction pipelining is the concept of overlapping operations.

- Processors may have tools to find possible dependencies among different evaluations and overlap instructions

- Even when they may have different number of stages and need differing amounts of time to perform the operations.

- 2. Processing features in contemporary parallel computations

- Superscalar processing

- Superscalar processors are designed to schedule instructions at runtime, typically without a compiler support.

- That means that the scheduling is dynamic.

Remind that , in contrast to this, the VLIW processors (explicit descriptions what to do with the bundle) schedule the instructions by the compiler preprocessing at compile time.

- 2. Processing features in contemporary parallel computations

- Out-of-order execution

- Data may not be available in registers when needed

- Out-of-order execution may avoid the stalls due to the slow communication withing memory hierarchy.

- Reorder buffer stored instructions that can be executed once their operands are available.

- 2. Processing features in contemporary parallel computations

- Multiple functional units

- advantages (parallelism) versus disadvantages (difficult to exploit)

- Standard on chips, in cores

- Processor arrays

- ▶ ILLIAC IV (1972) with 64 elementary processors

- concept behind the graphic processing units (GPU)

- Hybrid stuff: multicore and manycore processing

- Multicore processors with tens of cores

- Manycore processors with hundreds of cores

- Specific control needed: simultaneous multithreading (SMT)

(hyperthreading) more threads and schedule executable instructions

from different threads and that can be even from different processes in

the same cycle. It is a thread analogy of superscalar processing.

- Considering a chip with more cores as a bundle of logical processors.

### 3. Summarizing recent history of parallel computing in a few slogans

Seventies of the 20th century were characterized by data pipelining and vector computations in general,

### 3. Summarizing recent history of parallel computing in a few slogans

- Seventies of the 20th century were characterized by data pipelining and vector computations in general,

- Eighties can be considered as a revival of computer architectures with reduced instruction sets and strong integer arithmetic,

### 3. Summarizing recent history of parallel computing in a few slogans

- Seventies of the 20th century were characterized by data pipelining and vector computations in general,

- Eighties can be considered as a revival of computer architectures with reduced instruction sets and strong integer arithmetic,

- Nineties started with practical use of multiprocessors and several very successful massive parallel systems and

### 3. Summarizing recent history of parallel computing in a few slogans

- Seventies of the 20th century were characterized by data pipelining and vector computations in general,

- Eighties can be considered as a revival of computer architectures with reduced instruction sets and strong integer arithmetic,

- Nineties started with practical use of multiprocessors and several very successful massive parallel systems and

- Later we saw a widespread use of hybrid and massively parallel computational tools.

- Memory hierarchy: general view

- ▶ speed × respond time × cost

- registers (very high-speed memory accessible by computational units)

- cache (locally accessible high-speed memory)

- main memory gigabytes, access speed around units of GB/s

- disc storage terabytes, access speed around hundreds of MBytes/s

- memory available via network etc.

The gap increases exponentially

- Memory components/functionality

- Physical address: actual address where data is stored

- Memory components/functionality

- Physical address: actual address where data is stored

- ► Logical (virtual) address: address generated by CPU(s). Logical addresses can span much larger space called virtual memory.

- Memory components/functionality

- Physical address: actual address where data is stored

- ► Logical (virtual) address: address generated by CPU(s). Logical addresses can span much larger space called virtual memory.

- Memory management units does the translations between physical and logical addresses using relocation register.

- Memory components/functionality

- Physical address: actual address where data is stored

- ► Logical (virtual) address: address generated by CPU(s). Logical addresses can span much larger space called virtual memory.

- Memory management units does the translations between physical and logical addresses using relocation register.

- Paging: scheme to manage exchanges of memory needed by computations caused by different logical and physical memory. Splits data into chunks of fixed size that can be easily indexed and exchanged.

- Memory components/functionality

- Physical address: actual address where data is stored

- Logical (virtual) address: address generated by CPU(s). Logical addresses can span much larger space called virtual memory.

- Memory management units does the translations between physical and logical addresses using relocation register.

- Paging: scheme to manage exchanges of memory needed by computations caused by different logical and physical memory. Splits data into chunks of fixed size that can be easily indexed and exchanged.

- Segmentation is another way of logical address indexing alternative to paging, uses variables size data chunks. Slower, but avoids inner fragmentation.

- 2 Memory components/functionality

- Physical address: actual address where data is stored

- Logical (virtual) address: address generated by CPU(s). Logical addresses can span much larger space called virtual memory.

- Memory management units does the translations between physical and logical addresses using relocation register.

- Paging: scheme to manage exchanges of memory needed by computations caused by different logical and physical memory. Splits data into chunks of fixed size that can be easily indexed and exchanged.

- Segmentation is another way of logical address indexing alternative to paging, uses variables size data chunks. Slower, but avoids inner fragmentation.

- ► Swap space: substitutes for (smaller) physical memory. Enables to use much larger logical space. Swap in × swap out.

- Memory components/functionality

- Memory thrashing: problem when the computation spends a lot of time with data exchanges between physical and logical space. This may strongly slow down computations adding this data manipulation overhead.

- Memory components/functionality

- Memory thrashing: problem when the computation spends a lot of time with data exchanges between physical and logical space. This may strongly slow down computations adding this data manipulation overhead.

- Page fault represents the situation when data page is not available for a computation and should be retrieved from other (lower) levels of memory hierarchy. Similarly for segments.

### 4. Computer memory issues

Very fast memory: cache: low-latency high-bandwidth storage. From the hardware point of view: main memory typically assembled from DRAM (dynamic random access memory) chips, cache uses SRAM (static random access memory): fast access, but smaller capacity per area.

Sketch of a typical cache hierarchy:

- ▶ Level 0 (L0) Micro operations cache

- ► Level 1 (L1) Instruction cache (kBytes)

- Level 1 (L1) Data cache (kBytes)

- Level 2 (L2) Instruction and data cache (MBytes)

- ▶ Level 3 (L3) Shared cache

- Level 4 (L4) Shared cache

### 4. Computer memory issues: cache terminology

- Cache hit: processor has found data ☺

- Cache miss: not the previous case, measured by miss-ratio ©

- Cache blocks, lines express the cache structure

- Cache write policy

- Write-through; data are (pseudo)simultaneously updated both in cache and memory.

- Write-back (write-deferred); data are update only in cache. Later in memory.

- We need cache sharing: sharing data for computational units in the same cache lines

- We need to avoid cache thrashing: degradation of performance due to insufficient caches

## 4. Computer memory issues: cache terminology

- Cache mapping: similarly as mapping between pages and memory, cache must have some mapping policy

- Directly mapped caches map memory blocks only to specific cache locations.

- Fully associative caches can map the memory blocks to any cache position. Associative memory used to store content and addresses of the memory word.

- Compromise solution between directly-mapped and fully associative caches are set associative caches. It is an enhanced form of direct mapping.

#### 4. Other computer memory issues

- Why memory management?

- Minimize fragmentation (remember pages and segments), keep track of allocated and deallocated data chunks, keep data integrity

- Difficult for multiprocessors.

- Interleaving memory using memory banks

- A way to decrease memory latency

- The interleaving is based on the concept of memory banks of equal size that enable to store logically contiguous chunks of memory as incontiguous vectors in different parts of memory using a regular mapping pattern.

- Example of Cray-2

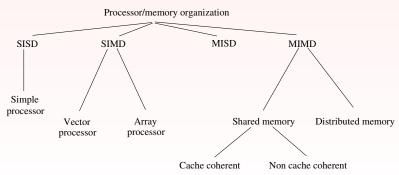

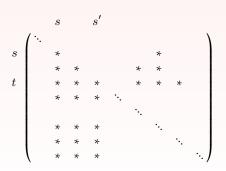

#### 5. Taxonomy of architectures by Flynn

Simple macro classification of parallel computers proposed by Flynn. It considers main features of computers represented by data and control flows. Used acronyms represent by S the word single, by I the word instruction, by M the word multiple and by D the word data.

- SISD: single instruction single data stream

- traditional (von Neumann) single CPU processor (computer)

- extinct type of architectures (but useful as a model)

- sometimes called uniprocessor in order to emphasize SISD character (that virtually does not exist)

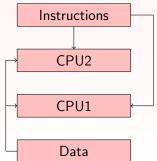

- MISD: multiple instruction single data stream

- useful feature, but full such architectures mostly experimental difficult to have the whole architecture based on this principle and having it efficient

- example: single data: angle, computing  $\sin(angle) + \cos(angle)$ .

- some MISD architectures useful as computers that compute and detect/mask errors for a single data stream

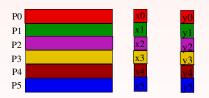

- SIMD as a prevailing principle

- vectorization

- matrix processors

- supercomputers

- 6 MIMD: multiple instruction multiple data streams

- the most general case, prevailing now

- any interconnection for sending data and instructions, in general

- Cosmic Cube built at Caltech in 80's, Cray X-MP/2

- ▶ iPSC 860 by Intel

- needed cache coherence:

- ★ achieving uniformity and consistency of shared data that can be distributed over more local caches

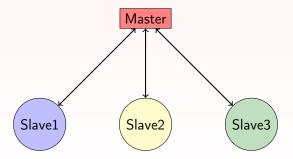

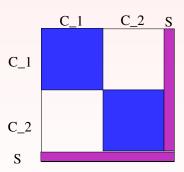

- (continued) Other possible classification of MIMDs:

- By memory access (local/global caches, shared memory caches, cache only memory, distributed (shared) memory),

- by topology and interconnection (master/slave, crossbar, pipe, ring, array, torus, tree, hypercube, ...).

#### 5. Taxonomy of architectures by Flynn

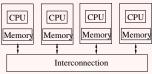

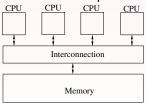

Multicomputers - MIMD computers with distributed memory: clusters, grid systems

Multiprocessor systems - MIMD computers with shared memory

Hybrid heterogenous multiprocessor systems

#### 6. Interconnection network and routing

- Interconnection network (IN, interconnection, interconnect) physically connects different components of a parallel computer but it can describe an outer network as well.

- Its topology describes the actual way how the modules (nodes, memories etc.) are connected to each other. The topology can be static or dynamic.

- Routing describes the way how the modules exchange information.

The routing can be described as a union of two components.

#### 6. Interconnection network and routing

# A. Static (and possibly also dynamic) interconnections The main issues and concerns

- pure connectivity: how many links are used to connect nodes, minimum, maximum, weakest points

- connectivity for communication: lengths of interconnecting paths.

- cost, static and dynamic complexity of interconnection

- extensibility: important mainly for reconfigurable architectures (as home-made clusters)

All these items have implications for bandwidth and latency

### 6. Interconnection network and routing

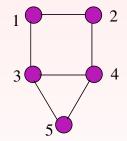

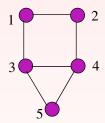

#### A. Static interconnections

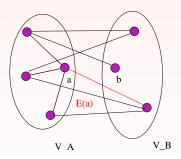

Standard model for static interconnection networks is a graph, often undirected since the interconnecting lines can be often used in both directions. Its few characteristics:

Diameter is a maximum distance between any pair of graph nodes.

Distance of two nodes in a graph is the length of the shortest path between them.

## 6. Interconnection network and routing

#### A. Static interconnections

Standard model for static interconnection networks is a graph, often undirected since the interconnecting lines can be often used in both directions. Its few characteristics:

- Diameter is a maximum distance between any pair of graph nodes.

Distance of two nodes in a graph is the length of the shortest path between them.

- Bisection (band)width: minimum number of edges that should be removed to partition the graph into two parts of equal node counts

## 6. Interconnection network and routing

#### A. Static interconnections

Standard model for static interconnection networks is a graph, often undirected since the interconnecting lines can be often used in both directions. Its few characteristics:

- Diameter is a maximum distance between any pair of graph nodes.

Distance of two nodes in a graph is the length of the shortest path between them.

- Bisection (band)width: minimum number of edges that should be removed to partition the graph into two parts of equal node counts

- Degree of a node is the number of adjacent vertices.

#### 6. Interconnection network and routing

#### A. Static interconnections

Standard model for static interconnection networks is a graph, often undirected since the interconnecting lines can be often used in both directions. Its few characteristics:

- Diameter is a maximum distance between any pair of graph nodes.

Distance of two nodes in a graph is the length of the shortest path between them.

- Bisection (band)width: minimum number of edges that should be removed to partition the graph into two parts of equal node counts

- Degree of a node is the number of adjacent vertices.

- Node/edge connectivity is the number of nodes/edges that have to be removed to increase the number of components of the originally connected graph.

#### 6. Interconnection network and routing

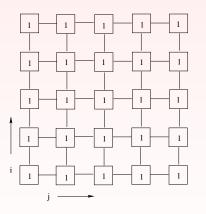

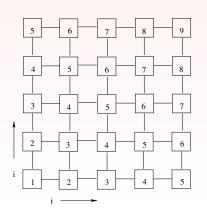

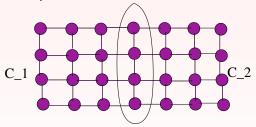

#### A. Static interconnections: examples

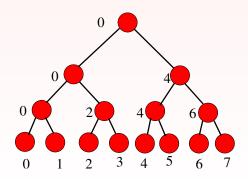

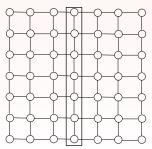

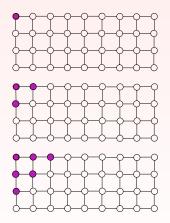

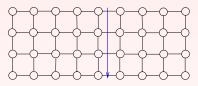

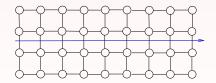

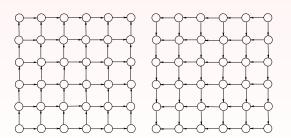

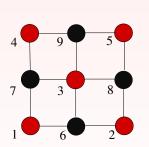

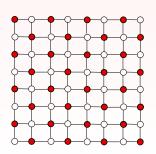

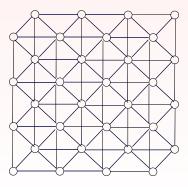

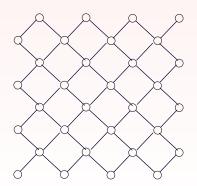

ullet a complete graph, linear graph, binary tree, fat tree as in CM-5, cycle, 2-dimensional mesh, 2-dimensional torus. An important case: a d-dimensional hypercube with  $2^d$  nodes.

| connection                | max deg    | diameter           | edge connect | bisect width        |

|---------------------------|------------|--------------------|--------------|---------------------|

| completely connected      | p-1        | 1                  | p-1          | $p^2/4$             |

| star                      | p-1        | 2                  | 1            | 1                   |

| binary tree $p = 2^d - 1$ | 3          | $2\log_2((p+1)/2)$ | 1            | 1                   |

| d-dimensional mesh        | 2d         | $d(\sqrt{d}p-1)$   | d            | $p^{\frac{d-1}{d}}$ |

| linear array              | 2          | p-1                | 1            | 1                   |

| d-hypercube $p = 2^d$     | $\log_2 p$ | $\log_2 p$         | $\log_2 p$   | p/2                 |

#### 6. Interconnection network and routing

#### A. Static interconnections

One could prefer, for example:

- small diameter of the static interconnection,

- large bisection bandwidth,

- large connectivity or

- small average node degree.

## 6. Interconnection network and routing

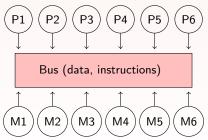

#### B. Dynamic interconnections

- Bus

- Set of communicating lines that connect modules.

- Unidirectional, bi-directional, separate instruction and data lines

- Efficient bus should contain at least two communication paths, one for instructions and the other one for computational data.

- 6. Interconnection network and routing

- B. Dynamic interconnections

- Bus

- Bounded bandwidth: limited number of nodes connected in practice.

- Constant time for an item of communication among limited number of nodes

- Consequently, scalable in cost but not scalable in performance.

## 6. Interconnection network and routing

#### B. Dynamic interconnections

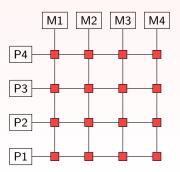

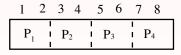

- 2 Dynamic networks with switches (crossbar networks)

- Interconnection network that completely interconnects processing elements with other modules using a set of switches.

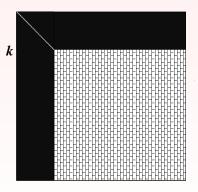

- For simplicity, assume p (P1-Pp) processing elements and m (M1-Mm) memory banks.

#### 6. Interconnection network and routing

#### B. Dynamic interconnections

- 2 Dynamic networks with switches (crossbar networks)

- $p \times m$  switches needed. Then min(p,m) lines can work in parallel.

- Useful for small-scale parallel computers.

- Assuming  $m \ge p$  (more memory banks, reasonable practical assumption), complexity of the interconnection grows at least as  $\Omega(p^2)$ .

- Consequently: dynamic networks with switches are not scalable in cost.

- 6. Interconnection network and routing

- B. Dynamic interconnections

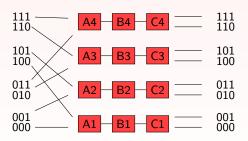

- Multistage interconnection networks

- Several stages of switches interconnected by communication lines

#### 6. Interconnection network and routing

#### B. Dynamic interconnections

- Multistage interconnection networks

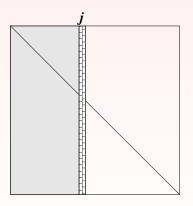

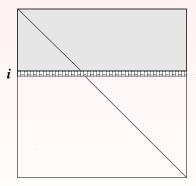

- ▶ Using *k* serially connected stages: a reasonable compromise.

- May have w nodes in a stage and more (t) links between two neighboring stages.

- ▶ Its transfer power can be expressed using the node degree is equal to

$$g = t/w$$

.

Connection can be expressed by a permutation

$$\pi: \{1, \dots, n\} \to \{1, \dots, n\}.$$

More scalable in cost than crossbar and more scalable than bus in performance

# 6. Interconnection network and routing B. Dynamic interconnections

- Multistage interconnection networks

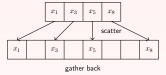

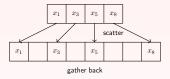

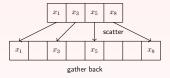

- Easy to code interconnections by binary inputs: basic types

- **★** perfect shuffle (circular shift left):  $000 \rightarrow 000$ ,  $001 \rightarrow 010$  etc.

- $\bigstar$  baseline: rotate last i+1 bits right

- $\bigstar$  butterfly interchange bits at positions 0 and i

- Should be synchronized with algorithms

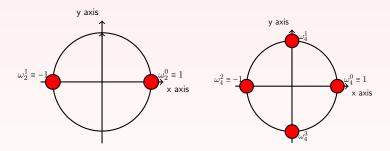

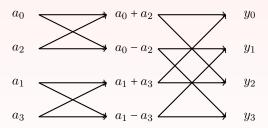

- Example: omega network: N elements,  $\log_2(N)$  stages, w = N/2 elements per stage, circular shift left

#### 6. Interconnection network and routing

#### B. Dynamic interconnections

- Fat tree interconnections

- Fat tree network with the topology of full binary tree.

- The number of actual connections between nodes at different (neighboring) levels increases in order to support "long distance" communications via the root of the network.

- Problems with mapping unstructured problems to a computer architecture with such interconnect

- CM5 computer

6. Interconnection network and routing

#### C. Routing and switching

Routing algorithms determine paths of messages between their sources and sinks.

## 6. Interconnection network and routing

- Routing algorithms determine paths of messages between their sources and sinks.

- Simple routing strategies: shortest path algorithm, randomly picked routing, dimension-based routing (in hypercube interconnnect topologies), flooding etc.: deterministic and adaptive algorithms.

## 6. Interconnection network and routing

- Routing algorithms determine paths of messages between their sources and sinks.

- Simple routing strategies: shortest path algorithm, randomly picked routing, dimension-based routing (in hypercube interconnnect topologies), flooding etc.: deterministic and adaptive algorithms.

- But: routing is closely connected to switching (see the stages in multistage interconnects) where switching may take place.

## 6. Interconnection network and routing

- Routing algorithms determine paths of messages between their sources and sinks.

- Simple routing strategies: shortest path algorithm, randomly picked routing, dimension-based routing (in hypercube interconnnect topologies), flooding etc.: deterministic and adaptive algorithms.

- But: routing is closely connected to switching (see the stages in multistage interconnects) where switching may take place.

- Switches are devices that connect components of the interconnect together. They manage the data flow across the interconnect.

## 6. Interconnection network and routing

- Routing algorithms determine paths of messages between their sources and sinks.

- Simple routing strategies: shortest path algorithm, randomly picked routing, dimension-based routing (in hypercube interconnnect topologies), flooding etc.: deterministic and adaptive algorithms.

- But: routing is closely connected to switching (see the stages in multistage interconnects) where switching may take place.

- Switches are devices that connect components of the interconnect together. They manage the data flow across the interconnect.

- Switching strategy includes strategies message processing in switches

### 6. Interconnection network and routing

- Routing algorithms determine paths of messages between their sources and sinks.

- Simple routing strategies: shortest path algorithm, randomly picked routing, dimension-based routing (in hypercube interconnnect topologies), flooding etc.: deterministic and adaptive algorithms.

- But: routing is closely connected to switching (see the stages in multistage interconnects) where switching may take place.

- Switches are devices that connect components of the interconnect together. They manage the data flow across the interconnect.

- Switching strategy includes strategies message processing in switches

- For example, switching determines possible cutting of the messages transferred by an interconnection network into pieces.

#### 6. Interconnection network and routing

- Routing + switching: should be considered together

- Both they determine overall communication between sources and sinks (destinations), splitting messages and the manner of sending the messages from one node to another.

- Strategies to resolve interconnect conflicts: avoiding deadlocks

- Further development: better message aggregation, communication granularity, communication regularity needed

#### 6. Interconnection network and routing

#### C. Routing and switching

- Timing models needed to consider routing and switching together

- bandwidth of a connection mentioned above is a maximum frequency at which data can be communicated in bytes per second

- Its inverse is called the byte transfer time

- ► The transport latency (for m words)

$$T(m) = T_{startup} + T_{delays\_on\_the\_route} + T_{finish} + T_{word} m.$$

Simplified:

$$T(m) = T_{transport\_latency} + T_{word} m.$$

# 6. Interconnection network and routing Routing and switching

- Routing with circuit switching

- Setting up and reserving a dedicated communicating path (channel, circuit). This path is guaranteed for the whole transmission in advance.

- Bandwidth fixed. Circuit switching can be also classified as connection-oriented.

- ► The path is set up by sending small control probe messages.

- No packets (typically), no buffers, (dedicated) circuit kept all the time. The communication time model: *l* links, message of size *m*:

$$T_{circuit}(m,l) = T_{overhead} + T_{control\_message} \, l + T_{word} \, m.$$

Useful for long messages, not communicated often.

# 5. Interconnection network and routing Routing and switching

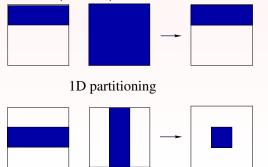

- Store-and-forward routing/switching (with packets)

- ► Message split into packets can be transmitted over different paths.

- The packets carry in its header the control information used to determine the path. In contrast to the routing with circuit switching, transfer time increases with the number of switches passed.

- Most general way of sending using more links.

- ► Intermediate node store received packets before passing them on.

- Errors can be checked on the way.

- Time for sending a message (transport latency) is approximately (message size m in words, l links, byte transfer time  $T_{word}$ ):

$$T_{store-and-forward} \approx T_{overhead} + l T_{word} m$$

.

Additional latency: packetize time

# 6. Interconnection network and routing Routing and switching

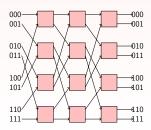

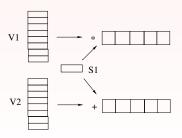

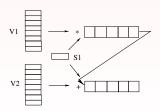

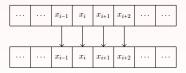

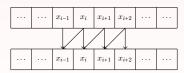

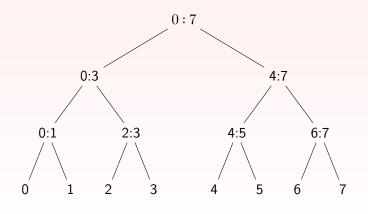

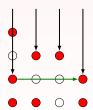

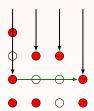

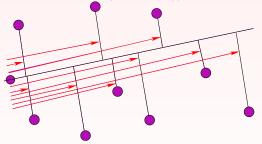

- Packet routing

- Uses pipelines

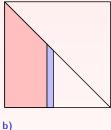

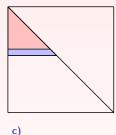

- Schematic difference between the store-and-forward routing and packet routing:

Store-and-forward routing (top) and packet routing that uses pipelining of the packets (bottom).

## Parallel computer architectures

# 6. Interconnection network and routing Routing and switching

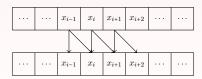

- Out-through routing with packets: an optimized packet routing

- Only one way for a packet

- Extends the idea of pipelining

- First a tracer establishes the connection

- Message is broken into fixed size units called flow control digits (flits)

with much less control information than packets. This implies that the

flits can be rather small.

- Typically in tightly coupled parallel computers with reliable interconnect that enables to make the error control information very compact.

- Possible to face a deadlock, for example, when sending messages in a circle and if some line is temporarily occupied.

### Parallel computer architectures

#### 6. Interconnection network and routing

Delivery schemes: relations sender(s)/receiver(s)

- Unicast: message to a specific node.

- Broadcast: one sender and multiple receiveres: one-to-all association

- Multicast: one-to-many-of-many, many-to-many-of-many

- Anycast: ②◎

## Parallel computer architectures

#### 6. Interconnection network and routing

#### More details on communication: blocking, synchronicity

- Blocking operations: Returns control to the calling process only after all resources (buffers, memory, links) are ready for next operations.

- Non-blocking operations: returns the control to the calling process after the operation has started and not necessarily finished. Strategies to avoid deadlocks needed.

- Synchronous communication: both sending and receiving process start the operation once the communication is set. (Often for shared-memory/SIMD systems.)

- Asynchronous communication: no such rule. A specific way message passing: synchronous or asynchronous depending on the computational algorithms and communicator possibilities.

#### Time models

A model for sequential time to compute n sequential operations

$$T_{seq} = n * (T_{seq\_latency} + T_{flop}),$$

Simple parallel model

$$T_{par} = T_{par\_latency} + \max_{1 \le i \le p} ((T_{flop})_i)$$

- Remind: three main timing aspects that should be taken into account.

- Bandwidth that limits the speed of communication

- Latencies of various kinds

- Time to perform numerical operations with data

### Speedup S

• The power of parallel processing with respect to purely sequential processing is often measured by the speedup.

$$T_{seq}/T_{par}$$

- Variations may consider related latencies.

- ullet Multiprocessors with p processors typically have

$$0 < S \le p$$

,

• Pipelining:

$$S = n * p/(n+p) \sim p,$$

More detailed:

$$S = n * p * T_{seq} / (T_{vec\_latency} + (n + p) * T_{vec\_op}).$$

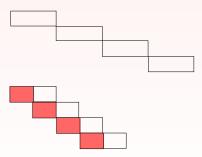

### Time models: Speedup S

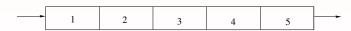

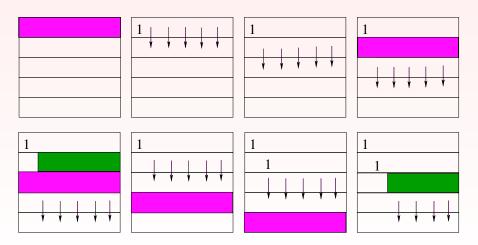

Graphical demonstration of data pipelining speedup for p = 5 processing the vector

$$a = \begin{pmatrix} a_1 & a_2 & \dots & a_n \end{pmatrix}$$

is

| time | segment1 | segment 2 | segment3 | segment 4 | segment 5 |

|------|----------|-----------|----------|-----------|-----------|

| 1    | $a_1$    |           |          |           |           |

| 2    | $a_2$    | $a_1$     |          |           |           |

| 3    | $a_3$    | $a_2$     | $a_1$    |           |           |

| 4    | $a_4$    | $a_3$     | $a_2$    | $a_1$     |           |

| 5    | $a_5$    | $a_4$     | $a_3$    | $a_2$     | $a_1$     |

|      |          |           |          |           |           |

Time models: Speedup S

•

$$S_p = T_1/T_{par},$$

• Efficiency:

0

$$0 < E \leq 1,$$

#### Time models: Amdahl's law

- Amdahl's law expresses a natural surprise over the fact that if a

process performs part of the work quickly and part of the work slowly

→ overall (speedup, efficiency) strongly limited by the slow part.

- ▶ f: fraction of the slow (sequential) part

- (1-f): the rest (parallelized, vectorized)

- ▶ t: overall time

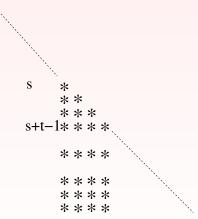

$$S = \frac{f * t + (1 - f)t}{f * t + (1 - f) * (t/p)} \le \frac{1}{f}$$

f

sequential

parallel

Overall: significant simplification (missing dependency on the problem size, actual search space etc.)

### **Scalability**

- Program (code) is scalable if larger efficiency comes with larger amount of parallelism

- linear, sublinear, superlinear efficiency.

- Superlinear: may be due to architecture/memory effects, much more typical is sublinear efficiency

- Specialized definitions of scalability in specific cases

Scalability: more practical classification

#### Scalability: more practical classification

• Consider solution time varying with the number of processors for a problem with a fixed total size. The code is (approximately) strongly scalable if the speedup is (approximately) equal to p (number of processing elements). That is, the code is strongly scalable, if  $T_{par} = T_{seq}/p$ . Strong scalability is often difficult to achieve for large p because of the communication.

#### Scalability: more practical classification

- Consider solution time varying with the number of processors for a problem with a fixed total size. The code is (approximately) strongly scalable if the speedup is (approximately) equal to p (number of processing elements). That is, the code is strongly scalable, if  $T_{par} = T_{seq}/p$ . Strong scalability is often difficult to achieve for large p because of the communication.

- Consider solution time varying with the number of processors for a

problem having a fixed size per processor. The code is (approximately)

weakly scalable if the code run time stays constant when the workload

is increased proportionally to the number of processors. In contrast to

the strong scalability, the weak scalability is often easier to be

achieved.

### Outline

- Foreword

- 2 Computers, computing, communication

- Parallel computing

- 4 Parallel processing and us parallel programming

- 5 Parallel computer architectures: hardware and classification

- 6 Combining pieces together: computational models

- Uniprocessor model

- Vector and SIMD model

- Multiprocessor model

- Parallelizing problems

- 8 Sparse data decomposition: graph partitioning

- 9 Factorizations

- 10 Parallel and parallelized algebraic preconditioning

$Algorithms \rightarrow {\rm architecture\_aware\_implementations} \rightarrow Computers$

- Idealized uniprocessor.

- latencies processor-memory

- possible superscalar processing, concurrent data movement

- threads to be quickly switched

- instruction pipelining (tacitly assumed)

- Idealized uniprocessor.

- latencies processor-memory

- possible superscalar processing, concurrent data movement

- threads to be quickly switched

- instruction pipelining (tacitly assumed)

- Idealized processor with data pipeline (vector processor; idealized SIMD computational model)

- Also data pipelining

- Sparse data from the point of view of access and pipelining

- their storage schemes

- more threads for possible concurrency

- Idealized uniprocessor.

- latencies processor-memory

- possible superscalar processing, concurrent data movement

- threads to be quickly switched

- instruction pipelining (tacitly assumed)

- Idealized processor with data pipeline (vector processor; idealized SIMD computational model)

- Also data pipelining

- Sparse data from the point of view of access and pipelining

- their storage schemes

- more threads for possible concurrency

- Idealized computers with more processors (MIMD)

- many more concepts, the highest dependence on architecture

- data/algorithm granularity

- problem partitioning

- load balancing

- multicore, manycore

Uniprocessor model

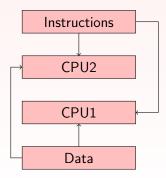

#### von Neumann architecture

- There is no pure uniprocessor nowadays. Even a simple Pentium III has on-chip and in its firmware:

- instruction level parallelism (up to 3 instructions)

- pipeline (at least 11 stages for each instruction)

- fine-grained data parallelism (SIMD type) like MMX (64bit) and SSE (128bit)

- more threads at system level for more cores

- What can be influenced by us?

What can be influenced by us?: ways to hide latencies

• Mostly: algorithm related items

#### What can be influenced by us?: ways to hide latencies

- Mostly: algorithm related items

- Code should be restructured so that

- caches can be used efficiently

- dynamic-out-of-order scheduling is enabled (may need tiny register/cache workspace)

- strong multithreading with more threads that can be fast switched is possible

- prefetching is easy (this is preparing data to be understood that they will be used soon)

What is typically outside our control: the rest ☺

Low-level control of data pipelines that is an ability to issue more (data processing) instructions at the same time that need

### What is typically outside our control: the rest ©

- Low-level control of data pipelines that is an ability to issue more (data processing) instructions at the same time that need

- Detecting true data dependencies: dependencies in processing order

### What is typically outside our control: the rest ©

- Low-level control of data pipelines that is an ability to issue more (data processing) instructions at the same time that need

- Detecting true data dependencies: dependencies in processing order

- Detecting resource dependencies: competition of data for computational resources

### What is typically outside our control: the rest ☺

- Low-level control of data pipelines that is an ability to issue more (data processing) instructions at the same time that need

- Detecting true data dependencies: dependencies in processing order

- Detecting resource dependencies: competition of data for computational resources

- Reordering instructions: most processors enable out-of-order scheduling

### What is typically outside our control: the rest ☺

- Low-level control of data pipelines that is an ability to issue more (data processing) instructions at the same time that need

- Detecting true data dependencies: dependencies in processing order

- Detecting resource dependencies: competition of data for computational resources

- Reordering instructions: most processors enable out-of-order scheduling

- Solving branch dependencies that can be performed by various ways

- ★ speculative scheduling across based on the assumption that typically every 5th-6th instruction is a branch

- ★ compile time scheduling. Can be helped by VLIW and well-chosen threads.

- ★ superscalar scheduling

- Codes should be flexible to this.

The following example indicates how the above-mentioned features can be enabled.

### Example

#### Consider a uniprocessor:

- clock frequency 2GHz,

- $\bullet$  main memory: DRAM with latency  $0.1 \mu s$ ,

- two FMA (floating-point multiply-add) units enabling 4-way superscalar processing (4 instructions in a cycle, e.g., two adds and two multiplies),

- two (double precision) words (each of 8 bytes) are obtained in a fetch, that is within the latency time.

- this means: 2 data fetches for 4 operations.

#### Case 1: No effort to minimize memory latency

- The clock cycle time: =  $1/frequency \equiv 1/(2.10^9)s = 0.5 \ ns$

- Since the processor can theoretically process  $2 \times 10^9 \times 4$  instructions per second then the maximum processor rate is 8 GFLOPs.

- ullet The memory is much slower: every memory request needs 0.1  $\mu s$  wait time memory latency.

Example: a dot product of two vectors (of infinite length).

- One multiplication with two numbers and adding the result to the partial product (two operations) need then 1 fetch: 2 operations for a fetch  $(0.1\mu s)$  of two numbers.

- That is 2 operations /  $0.1\mu s \rightarrow 2 \times 10^7$  operations per second.

- This leads to the rate of 20 MFLOPs much smaller than the potential of the processor.

### Case 2: Hiding latency using cache

Example: A \* B = C, hiding latency by cache. Assume cache of size 64kB with latency of  $0.5 \ ns$ .

- The memory size needed to store one number is 8 bytes. The cache can store three matrices A,B and C of dimension 50:  $3 \times 50^2 \times 8 = 7500 \times 8 = 60000$  bytes.

- A matrix fetch of A and B: 5000 words, 8 bytes each. Due to the cache that can store the matrices, this needs  $5000/2 \times 0.1 = 250~\mu s$ . For the transfer considered only latency and not the bandwidth.

- Once the matrices are in cache, operations can be performed.

- Asymptotically,  $2n^3$  operations are needed. If the computer performs 4 operations per cycle, we need  $2\times50^3\times0.5~ns~(clock~cycle)~\times0.25=125000/4~ns\approx31~\mu s$

- This gives  $281 \mu s$

- Resulting rate is  $2 * 50^3/0.000281 \approx 890$  MFLOPs. Close to this if added moving C back to memory.

### Case 3: Hiding latency using multithreading

Algorithm (Matrix-vector multiplication: Standard dot products of rows of  $A \in R^{m \times n}$  with  $b \in R^n$ .)

Input: Matrix A.

Output: Row products.

- 1: **for** i = 1, ..., m **do**

- $2: \qquad r_i = A(i,:) * b$

- 3: end for

- Notice the code restructuring in terms of vectors (see above).

- Medium grain code

### Case 3: Hiding latency using multithreading

A multithreaded version of the previous multiplication (symbolically).

```

Algorithm (Matrix-vector multiplication: Multithreaded dot products of rows of A \in R^{m \times n} with b \in R^n.)

```

**Input:** Matrix A.

Output: Row products.

1: **for** i = 1, ..., m **do**

- Loop by rows

- 2:  $r_i = new\_thread(dot\_product, double, A(i,:), b)$

- 3: end for

- Possible asynchronicity in fetches/computation introduced.

#### Case 3: Hiding latency using multithreading: general notes

- In situations like above: more threads than cores/processors may be useful to hide slow communication/memory.

- But note that threads consume some amount of memory. And they

may share the same cache.

- Various modifications of multithreading on contemporary computers

- The optimal number of threads is strongly architecture-dependent.

#### Case 3: Hiding latency using multithreading (continued)

- More ways to support more threads processed by one chip

- ► Fine-grain multithreading (switch between threads on every cycle)

- Coarse-grain/block multithreading (switching among the threads can be based on I/O demands or long/latency operations)

Simultaneous multithreading (more instructions + more threads; parts

- Simultaneous multithreading (more instructions + more threads; parts of different threads share, for example, a superscalar unit)

- Combination of the techniques above; combined scheduling for more supescalar units.

- Predecesssor of using threads massively: VLIW as in Tera MTA (2002): interleaved multi-threading, no data cache, relying on threads switching

### Case 4: Hiding latency using prefetch

- Boosting performance by advancing fetches from slower parts of memory hierarchy

- Prefetch of instructions

- Prefetch of data

- Data for the prefetch need to be prepared/enabled. Possible use of prefetch processor.

Case 5: Data preparation: improving memory bandwidth and latency: locality and regularity

• spatial locality: data are spatially local if the data items stored close (at logically close positions) to the executed items are highly probable to be executed soon. In this case, the use of prefetch with high chance to improve execution.

# Case 5: Data preparation: improving memory bandwidth and latency: locality and regularity

- spatial locality: data are spatially local if the data items stored close (at logically close positions) to the executed items are highly probable to be executed soon. In this case, the use of prefetch with high chance to improve execution.

- Example: vectors, matrices

Improvements by storage schemes / coding

6: end for

#### Spatial locality and matrix layout

- Memory layout: physical access of memory should be compatible with the logical access

- Sometimes forced by programming language: like column major versus row major

```

Algorithm (Summing columns of A \in R^{m \times n}.)

Input: Matrix A.

Output: Resulting vector sum of the sums.

1: for i = 1, ..., m do

2: sum_i = 0

3: for j = 1, ..., n do

4: sum_i = sum_i + A_{ij}

5: end for

```

• Here: columnwise A is bad, rowwise A is good

Case 5: Data preparation: improving memory bandwidth and latency: locality and regularity

• temporal locality: Data are temporally local if the items recently executed have a high chance to be executed soon again. Such data can be "hanged" in registers or cache for a long time.

# Case 5: Data preparation: improving memory bandwidth and latency: locality and regularity

- temporal locality: Data are temporally local if the items recently executed have a high chance to be executed soon again. Such data can be "hanged" in registers or cache for a long time.

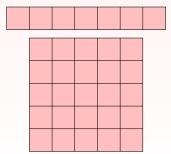

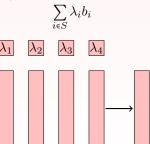

- Example: linear combination of a set of vectors  $b_i, i \in S$ . The coefficients  $\lambda_i$  have a high temporal locality being reused a couple of times within a short time

# Case 5: Data preparation: improving memory bandwidth and latency: locality and regularity

- regularity of processed data: this means that the code is often faster and easier to be processed by the computer software when composed from a set of similar and possibly standardized components

- Example: row/column blocks

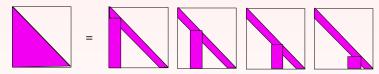

- Out-of-algorithm-scheme tiling: a technique that optimizes data accesses to minimize latencies (maximizing number of cache hits, often applied to loops)

- often applied to loops

- based on partitioning the data space, extremely important for sparse data

#### Catching more rabbits at the same time

- Coding to achieve localities and regularity

- Standardization: goals

- increase readability of codes and simplify software maintenance,

- improvements in code robustness,

- better portability, modularity and clarity,

- increase in effective memory bandwidth,

- creating a basis for machine specific implementations etc.

- Overall: BLAS1 set of subroutines / library (1970's) ( AXPY  $(\alpha x + y)$ , dot\_product  $(x^Ty)$ , vector\_norm, plane rotations, etc.)

- Other BLAS for keeping localities and regularity

- Further BLAS-like development: see below

### Vector and SIMD model

Vector and SIMD model

#### Vector processing basics

- Vectorization: one of the most simple methods to introduce parallelism into computations.

- Data pipelining and instruction pipelining are behind. Technically:

- vector registers for instructions

- vector registers for data

- Important for vector based machines/chips.

- Contemporary computers support vectorization as well on chips ( plus caches, multiple pipelines, SIMD instructions etc.)

- Vector machines may have better integration with computational units and memory.

- Necessary condition for a large-scale code vectorization: lack of dependency among (fine grain) data items.

#### Vector processing: some historical notes

- CDC series and and Cray computers: one of the most successful chapters in the development of parallel computers.

- A lot of early progress connected to Seymour Cray (1925 1996; father of supercomputing, chief constructor of latest model of CDC computers with some earliest parallel features, constructor of the first CRAYs: commercially successful vector computers (supercomputers) (Cray-1 (1976); Cray X-MP (1983); Cray C-90 (1991) etc.)

- In 70's memory-memory vector processors and (vector) register-register processors existed side by side. The latter prevail nowadays.

- Vector machines dominated in scientific computing until the advent of massively parallel machines.

#### Some vector processing principles and characteristics

- Vector supercomputers with typically different (multiplied) vector functional units / vector processing units for different operations.

- Load/store units may be also efficiently vectorized.

- Architecture includes also scalar units. Small efficiency of the scalar arithmetic → RISC workstations with efficient FPU+ALU.

#### Some vector processing principles and characteristics

How can be characterized processing on a vector (supercomputer) architectures.

- Some early indicators

- $R_{\infty}$ : computer speed (for example, in Mflops) on a vector of infinite length,

- $n_{1/2}$ : vector length needed to reach half of the speed  $R_{\infty}$ ,

- $n_v$  denotes the vector length needed to get faster processing than in the scalar mode.

#### Chaining: a way to overcome the length of vector registers

- Chaining represents a way of computation developed for early Crays (Cray-1 (1976), predecessor project STAR) and used since then.

- Based on storing intermediate results of vector pipelines, combining them possibly with scalar data and using them directly without communication with main memory: supervector performance.

- The process controlled by the main instruction pipeline. Closely related overlapping introduced for vector operations by Cray-1.

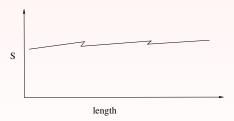

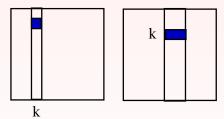

#### Stripmining: a consequence of supervector performance

- Long vectors split to parts of sizes less or equal to the vector register length allowed by vector registers and possibly other hardware components.

- The dependence of computer speedup on vector length is a saw-like curve depicting the effect of stripmining

Splitting long vectors for Cyber-205 (late 70's; memory-memory vector processor) scheduled by an efficient microcodes. Later done by hardware.

### Regular stride in codes: defence of coding

Processing vectors with a non-unit distance among entries in memory.

#### Regular stride in codes: defence of coding

- Processing vectors with a non-unit distance among entries in memory.

- If this distance is regular, it is called **stride** and vector processor does not need to be always efficient in processing vectors with strides > 1.

#### Regular stride in codes: defence of coding

- Processing vectors with a non-unit distance among entries in memory.

- If this distance is regular, it is called stride and vector processor does not need to be always efficient in processing vectors with strides > 1.

- BLAS routines can deal with various strides (but there is a price for it).

#### Regular stride in codes: defence of coding

- Processing vectors with a non-unit distance among entries in memory.

- If this distance is regular, it is called stride and vector processor does not need to be always efficient in processing vectors with strides > 1.

- BLAS routines can deal with various strides (but there is a price for it).

- ullet An example: a column in the following matrix stored by rows can be obtained by getting its entries with the stride 5

Vectorization

#### Vectorization examples

#### **Vector norm**

### Algorithm (Computing (squared) norm $x^Tx$ for $x \in \mathbb{R}^n$ .)

**Input:** Vector x.

Output: Resulting squared norm.

1: for  $i = 1, \ldots, n$  do

$2: x_i = x_i * x_i$

3: end for

- No dependence among the vector components.

- Automatic vectorization.

#### Vectorization examples

```

Algorithm (Product with forward shift x_{1:n-1} = x_{1:n-1}^T x_{2:n}.)

```

**Input:** Vector x.

**Output:**  $x_{1:n-1} = x_{1:n-1}^T x_{2:n}$ .

1: **for** i = 1, ..., n-1 step 1 **do**

$2: x_i = x_i * x_{i+1}$

3: end for

The loop vectorizes as well.

#### **Vectorization examples**

### Algorithm (Product with backward shift.)

**Input:** Vector x. **Output:** See below

1: **for** i = 2, ..., n step 1 **do**

2:  $x_i = x_i * x_{i-1}$

3: end for

• The loop does not vectorize:  $x_i = \prod_{j=1}^i x_j$ . (different than above).

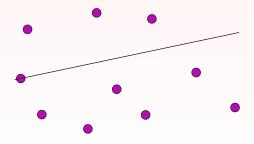

#### Vectorization examples

### Algorithm (Reversing order of processing.)

```

Input: Vector x.

Output: See below

1: for i = n, ..., 2 step -1 do

2: x_i = x_i * x_{i-1}

3: end for

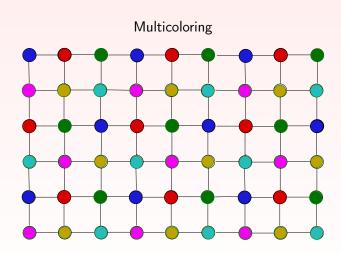

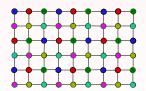

```